HDL Verifier从Simulink自动生成UVM组件和测试平台

2020年3月2日讯,MathWorks今天宣布,HDL Verifier从现已上市的Release 2019b开始提供对Universal Verification Methodology(UVM)的支持。HDL Verifier能够让开发FPGA和ASIC设计的设计验证工程师直接从Simulink模型生成UVM组件和测试平台,并在支持UVM的仿真器(比如来自Synopsys、Cadence和Mentor的仿真器)中使用这些组件和测试平台。

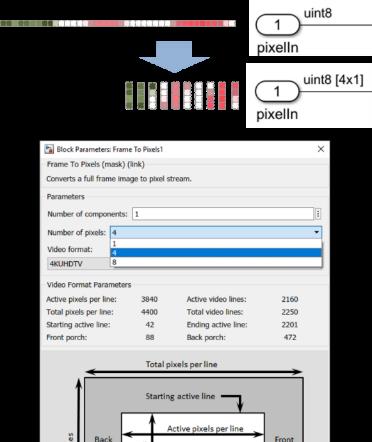

Wilson Research Group的一项最近研究发现,48%的FPGA设计项目和71%的ASIC设计项目依赖UVM进行设计验证。通常,算法开发人员和系统架构师在MATLAB和Simulink中开发新算法内容。然后,设计验证(DV)工程师在为RTL测试平台手工编写代码时使用MATLAB和Simulink模型作为参考,这一过程极其耗时。现在借助HDL Verifier,DV工程师可以从已经在Simulink中开发的系统级模型自动生成UVM组件,如序列或记分板。在为诸如无线通信、嵌入式视觉和控制等应用中使用的ASIC和FPGA设计而开发测试平台时,此方法可以减少验证工程师所花费的时间。

“借助Simulink,我们在手工编写生产UVM测试平台、测试序列和记分板上花费的时间可以减少大约50%,从而有更多时间专注于突破性创新应用。”Allegro MicroSystems的ASIC开发经理Khalid Chishti说,“我们针对汽车应用设计的ASIC依赖UVM进行生产验证,为这些设备开发算法曾是一项繁琐的任务,而MATLAB和Simulink对此进行了简化。”

HDL Verifier从Simulink模型生成UVM组件

HDL Verifier增添了一些新功能,例如,从MATLAB和Simulink中生成UVM组件、SystemVerilog断言和SystemVerilog DPI组件,现在可向负责ASIC和FPGA生产验证的设计验证团队提供更多扩展性支持。这些设计验证团队原本通过在SystemVerilog中手工编写代码,进而在HDL仿真器中开发严格测试平台,现在,他们能够从现有MATLAB和Simulink模型直接生成验证组件,并重用这些模型加快创建生产验证环境的速度。

“根据Wilson Research和Mentor Graphics的2018年功能验证研究,DV工程师在开发测试平台中花费在ASIC和FPGA项目上的时间,大约占他们工作时间的五分之一。”MathWorks首席HDL产品营销经理Eric Cigan说,“HDL Verifier能够从现有MATLAB和Simulink模型生成UVM和SystemVerilog DPI组件,不仅可以提高DV工程师的生产效率,而且会增进系统架构师、硬件设计师与DV工程师之间的合作。”

HDL Verifier R2019b现已在全球上市。

关于Allegro Microsystems

Allegro MicroSystems正在重新定义动力和传感技术的未来。从绿色能源到先进的机动和运动控制系统,我们的团队热衷于开发推动世界进步并给我们的客户带来竞争优势的智能解决方案。Allegro具有遍布全球的工程、制造和支持能力,是深受大型企业和区域市场领导者信任的合作伙伴。

关于MathWorks

MathWorks是数学计算软件的领先开发商。它所推出的MATLAB被称为“科学家和工程师的语言”,是一种用于算法开发、数据分析、可视化和数值计算的程序设计环境。Simulink是一个面向多域和嵌入式工程系统仿真和基于模型设计的框图环境。全球的工程师和科学家们都依赖于MathWorks公司所提供的这些产品系列,来加快在汽车、航空、电子、金融服务、生物医药以及其他行业的发明、创新及开发的步伐。MATLAB和Simulink产品也是全球众多大学和学术机构的基本教研工具。MathWorks创建于1984年,总部位于美国马萨诸塞州的内蒂克市(Natick, Massachusetts),在全球16个国家/地区拥有4500多名员工。